Imperial College London

## Imperial College

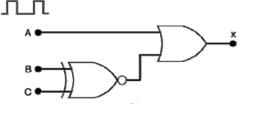

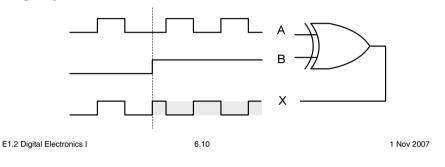

## Enable/Disable Circuits cont.

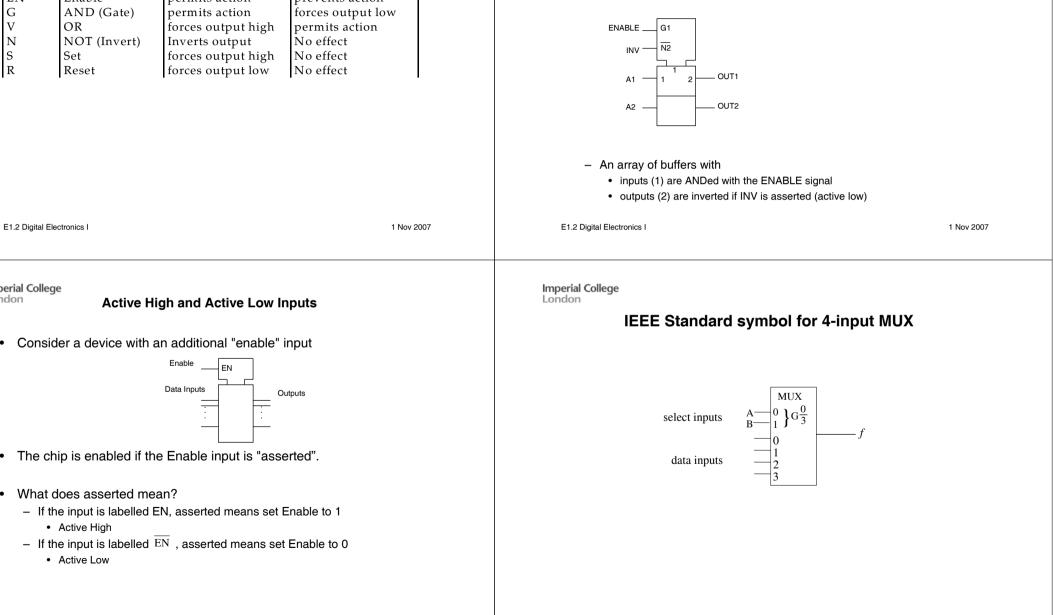

Design a logic circuit that will allow a signal to pass to the output only when control inputs B and C are both HIGH; otherwise, the output will stay LOW.

Design a logic circuit that will allow a signal to pass to the output only when one, but not both, of the control inputs are HIGH; otherwise, the output will stay HIGH.

E1.2 Digital Electronics I

Imperial College

6.9

Imperial College London

# **Merging & Inversion Circuits**

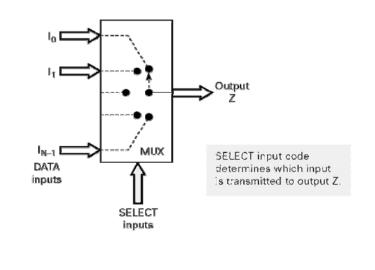

OR gate performs signal merging function:-

XOR gate performs selectable inversion function:-

Imperial College

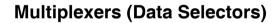

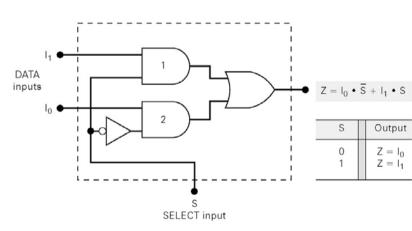

Two-input multiplexer.

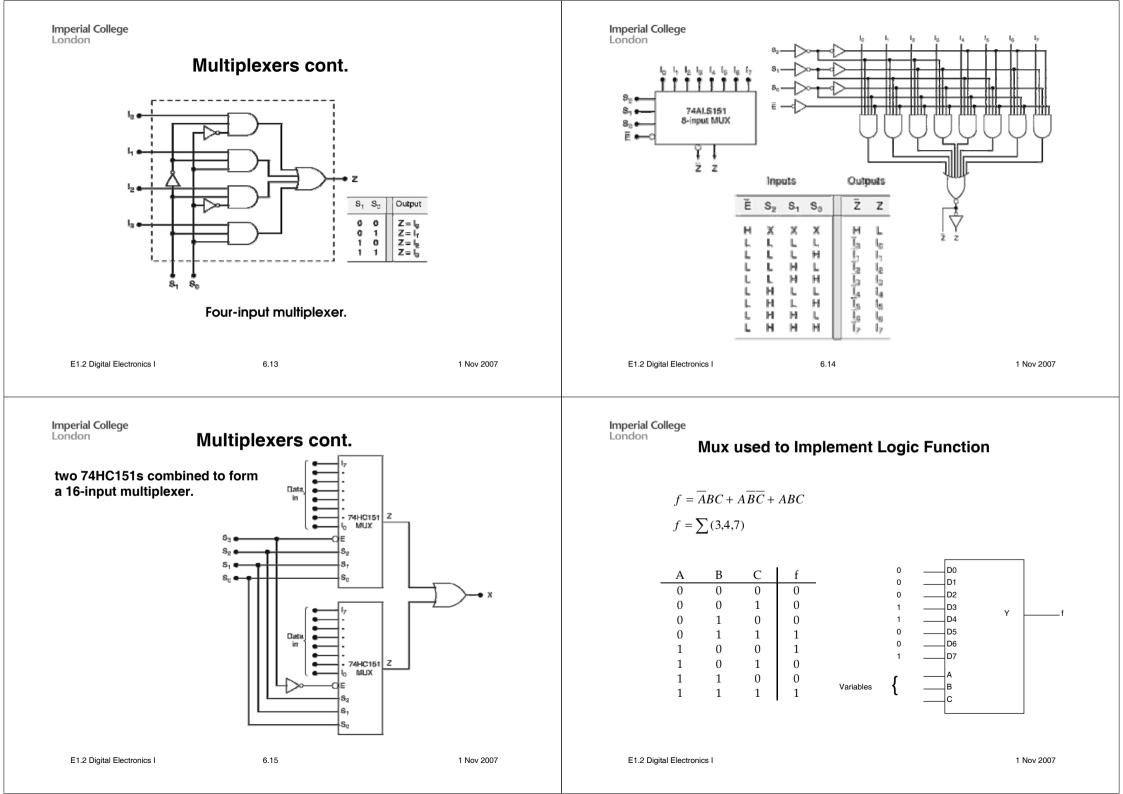

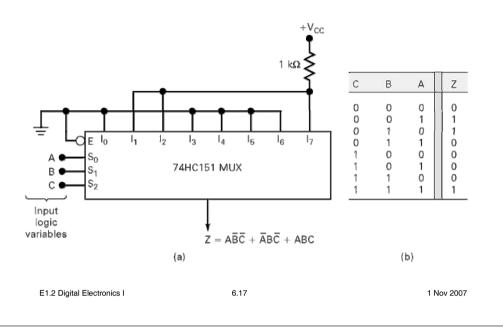

## Multiplexers cont.

1 Nov 2007

## Another example

Imperial College

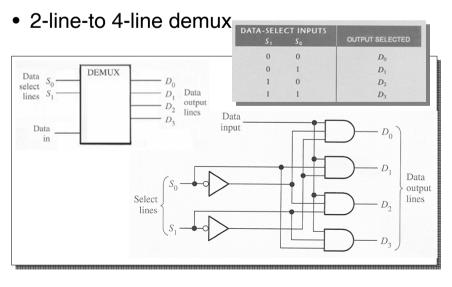

#### Demultiplexers

#### E1.2 Digital Electronics I

Imperial College London

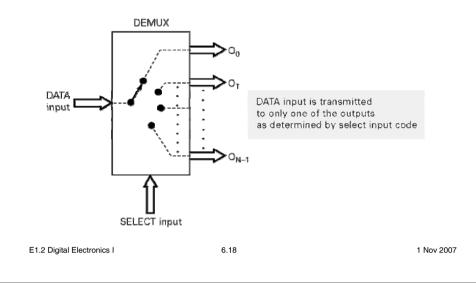

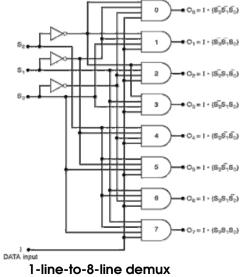

#### **Demultiplexers (Data Distributors)**

# A DEMUX takes a single input and distributes it over several outputs.

Imperial College

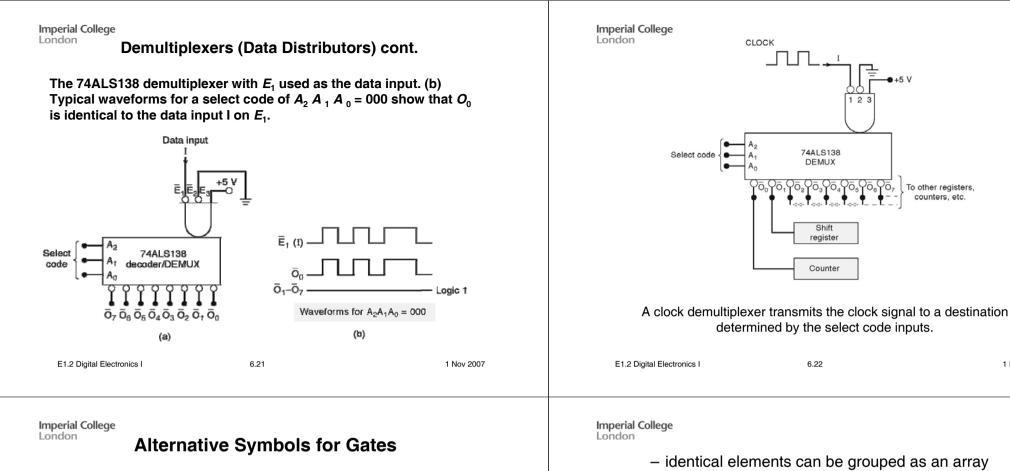

## Demultiplexers (Data Distributors) cont.

| SELECT code |                        |                | QUTPUTS |    |       |       |    |       |    |    |

|-------------|------------------------|----------------|---------|----|-------|-------|----|-------|----|----|

| $S_2$       | $\mathbf{S}_{\dagger}$ | S <sub>0</sub> | 07      | Oe | $O_5$ | $O_4$ | 09 | $O_2$ | о, | 00 |

| 0           | 0                      | 0              | 0       | 0  | 0     | 0     | 0  | 0     | 0  | ş  |

| 0           | 0                      | 1              | 0       | 0  | 3     | 0     | 0  | 0     | 1  | 0  |

| 0           | 1                      | 0              | 0       | 0  | 0     | 0     | 0  | 2     | 0  | 0  |

| 0           | 1                      | - 1            | 0       | 0  | 9     | 0     | 1  | 0     | -0 | 0  |

| 1           | 0                      | 0              | 0       | 0  | 8     | 1     | 0  | ø     | 0  | 0  |

| 1           | 0                      | 1              | 0       | 0  | 1     | 0     | 0  | 0     | 0  | 0  |

| 1           | 1                      | 0              | 0       | 1  | G     | 0     | 0  | 0     | 0  | 0  |

| 1           | 1                      | 7              | τ.      | 0  | 0     | 0     | 0  | 0     | 0  | 0  |

E1.2 Digital Electronics I

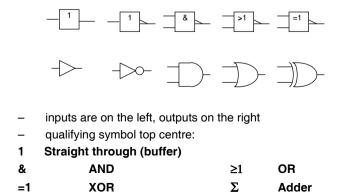

- The symbols presented so far are International Standards of ٠ ANSI and IEEE

- ٠ Other (older) symbols are still widely used

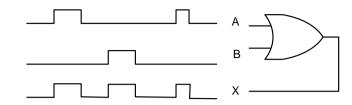

Multiplier

MUX

Multiplexer

Ρ

ΕN

A1

B1

A2

B2

A3

B3

A4

B4

with common control signals

enable signal

OUT1

OUT2

OUT3

OUT4

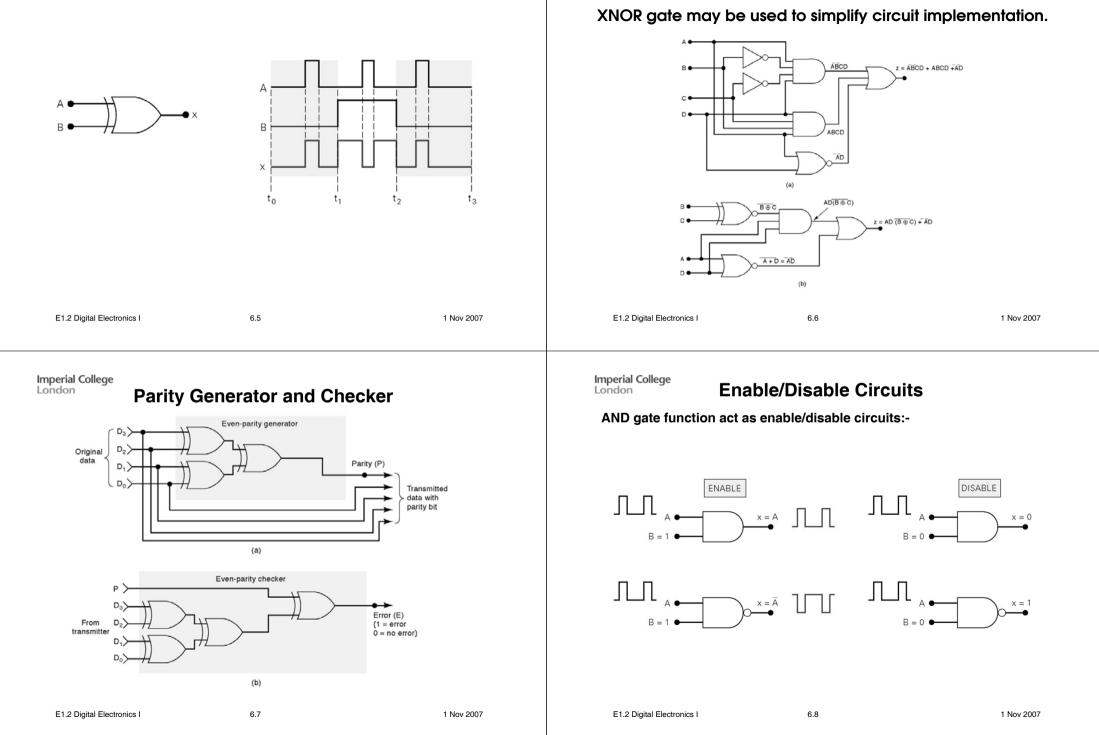

- Here is a 4 identical AND gates sharing a single

Δ1

B1

A2

B2

A3

B3

A4

B4

1 Nov 2007

To other registers,

counters, etc.

ō.

&

&

&

&

OUT1

OUT2

OUT3

OUT4

Imperial College London

Imperial College

London

٠

٠

٠

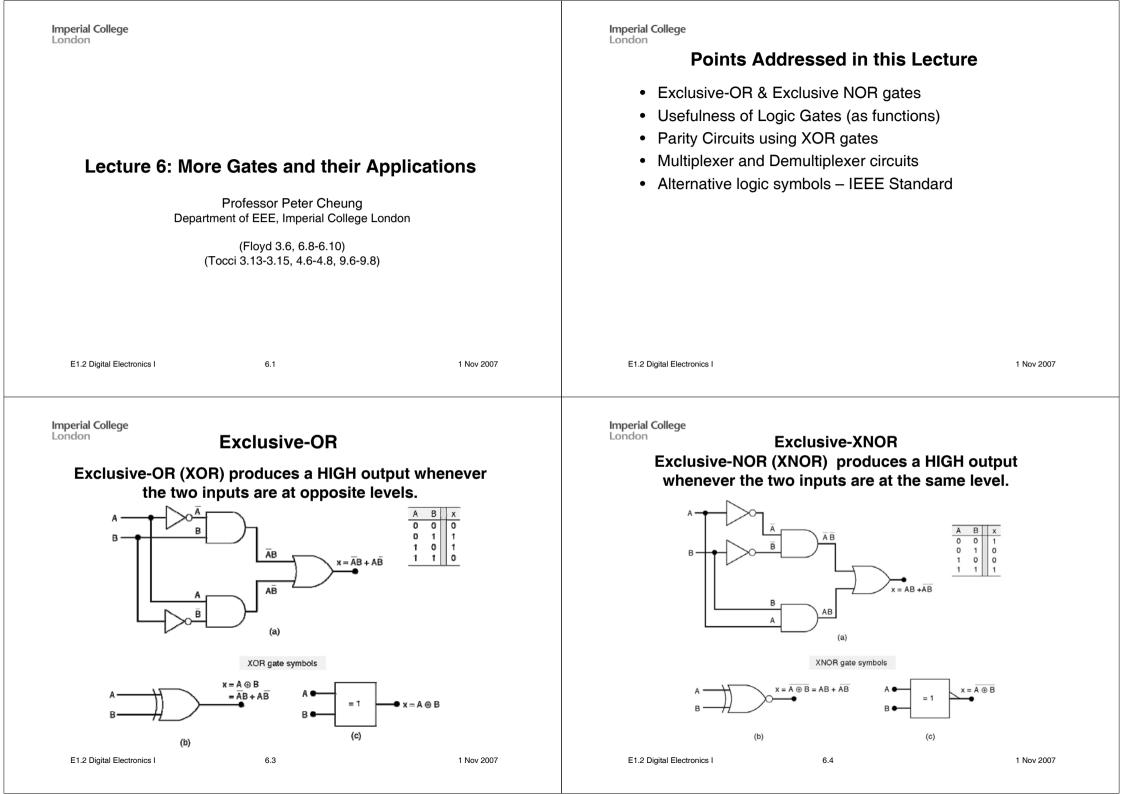

### • Other Dependencies

| Label | Name         | On assertion       | On de-assertion   |

|-------|--------------|--------------------|-------------------|

| EN    | Enable       | permits action     | prevents action   |

| G     | AND (Gate)   | permits action     | forces output low |

| V     | OR           | forces output high | permits action    |

| Ν     | NOT (Invert) | Inverts output     | No effect         |

| S     | Set          | forces output high | No effect         |

| R     | Reset        | forces output low  | No effect         |

#### Imperial College London

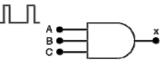

#### **Numbered Dependencies**

- Data inputs and outputs can be uniquely numbered •

- Control input dependency labels can be followed by a number •

- indicates which inputs or outputs they affect

- E.g.