## Lecture 8: ROM & Programmable Logic Devices

Professor Peter Cheung Department of EEE, Imperial College London

> (Floyd 10.1,10.3-5, 11.1-11.3) (Tocci 12.1, 12.4-5, 13.1-13.4)

## **Points Addressed in this Lecture**

- Read-only memory

- Implementing logic with ROM

- Programmable logic devices

- Implementing logic with PLDs

- Static hazards

| E1.2 Digital Electronics I                                                                                                                                                                                                                                                                               | 8.1                                             | Nov 2007 | E1.2 Digital Electronics I | 8.2                                                                                                                       | Nov 2007         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|

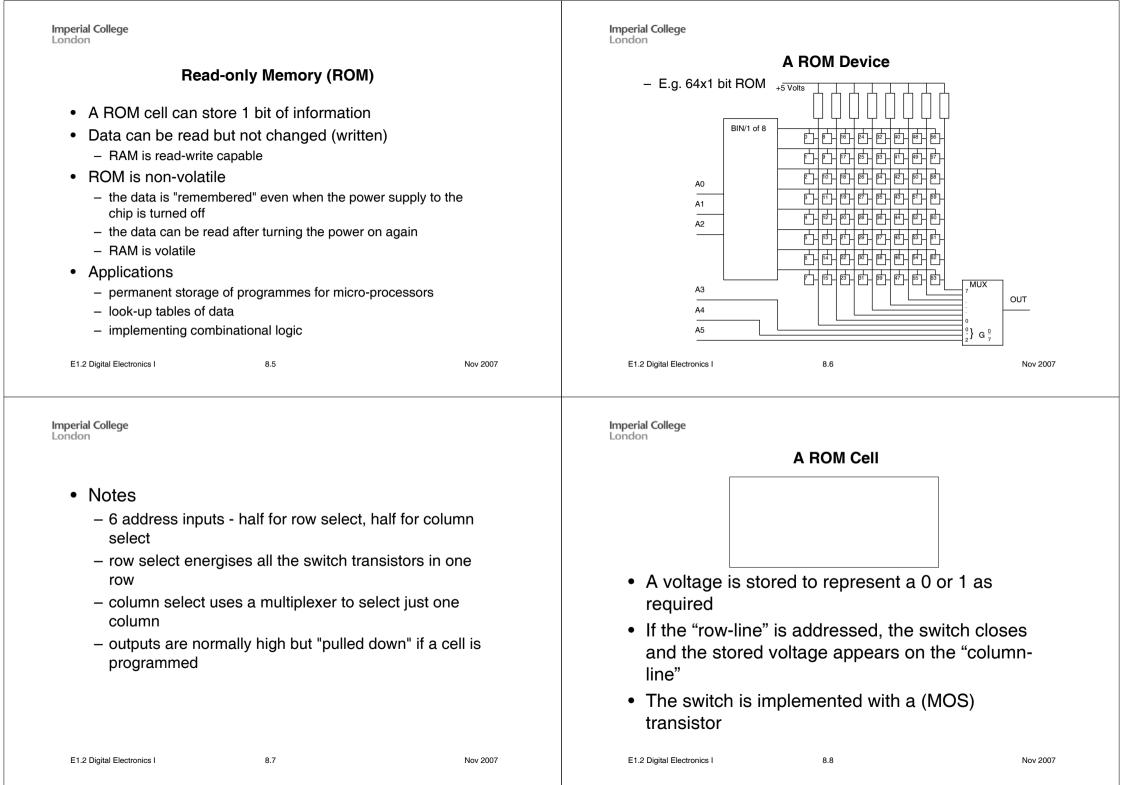

| Memory Cell: circuit<br>Memory Cell: circuit<br>Memory Word: 8 – 6<br>Byte: a group of 8 bir<br>Capacity (=Density)<br>- 4096 20-bit words<br>= 81,920 bits = 4096<br>- 1 M or 1 meg = 2 <sup>20</sup><br>- 1 G or 1 giga = 2 <sup>30</sup><br>Address<br>Read Operation (=fet<br>Write Operation (=set) | 54 bits<br>ts<br>*20 = 4K*20<br>etch operation) | ormation | Imperial College<br>London | Addresses<br>000 Word 0<br>001 Word 1<br>010 Word 2<br>011 Word 3<br>100 Word 4<br>101 Word 5<br>110 Word 6<br>111 Word 7 | 2<br>3<br>4<br>5 |

8.3

| Imperial College<br>London                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Imperial College<br>London                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

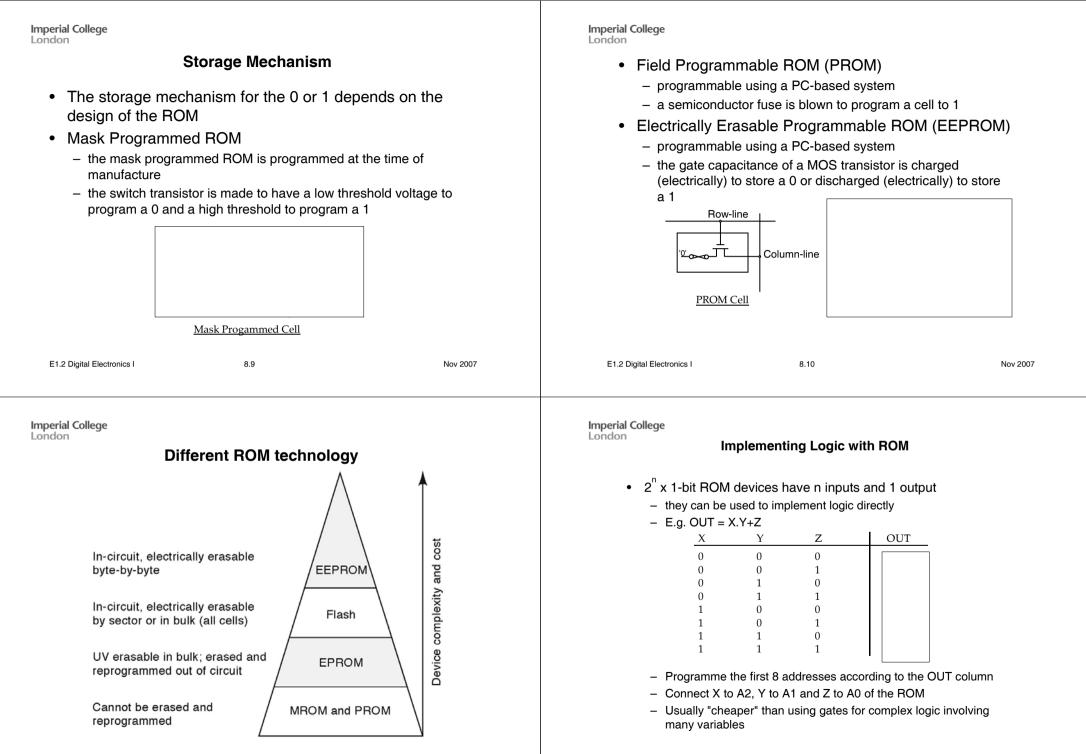

| <ul> <li>Summary of Combinational Logic Building Blocks</li> <li>Gates <ul> <li>seven basic gates from which all other circuits are made</li> <li>AND/NAND, OR/NOR, XOR/XNOR, NOT</li> </ul> </li> <li>Multiplexers <ul> <li>act as switches to connect one output to one of a number of input signals</li> <li>can also be used to implement logic</li> </ul> </li> <li>Decoders <ul> <li>inverted multiplexers (sometimes called demultiplexers)</li> <li>act as switches to connect one input to one of a number of output signals</li> <li>also includes circuits such as Binary to 7 Segment decoders</li> <li>four to seven bit decoders</li> </ul> </li> </ul> | <ul> <li>Arithmetic Circuits <ul> <li>binary adders, comparators, multipliers</li> <li>issues of signed or unsigned number representation are important</li> </ul> </li> <li>Programmable Logic Devices <ul> <li>ROMs</li> <li>implement arbitrary logic functions</li> <li>efficient for large combination logic circuits</li> <li>CPLDs</li> <li>implement canonical SOP Boolean expressions</li> <li>Advantages: <ul> <li>reduction in chip count</li> <li>easy upgrade by just reprogramming</li> <li>Disadvantages</li> <li>programming equipment required</li> </ul> </li> </ul></li></ul> |  |  |

| E1.2 Digital Electronics I 8.17 Nov 2007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | non-standard parts to stock and document E1.2 Digital Electronics I 8.18 Nov 2007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Imperial College<br>London<br>Static Hazards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Imperial College<br>London<br>Avoid Static Hazards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

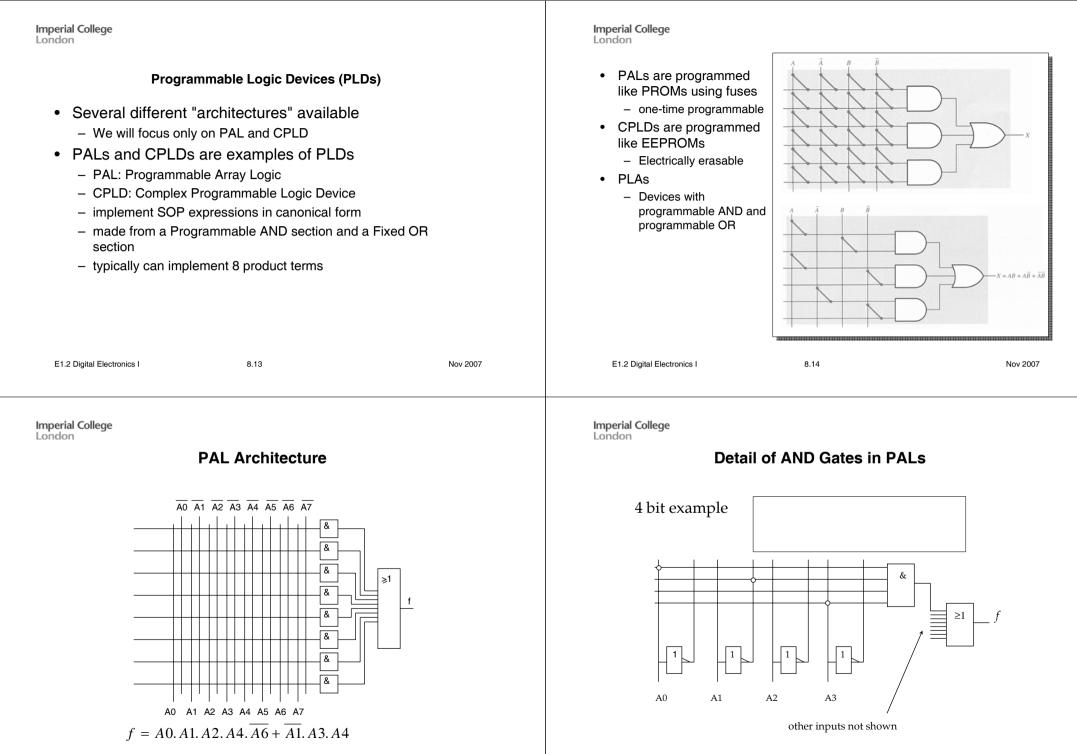

| • Gates have finite propagation delay<br>- This can cause glitches in logic waveforms<br>• Consider an inverter<br>- propagation delay of ~2nS<br>• E.g. Implementation of $f(A, B, C) = AB + \overline{A}C$<br>- If we use an inverter to generate $\overline{A}$ from $A$ then changes in $\overline{A}$<br>will be later than changes in $A$ .                                                                                                                                                                                                                                                                                                                     | • Using a Karnaugh map, look for groups of minterms which do NOT<br>overlap<br>- These are potential hazards<br>• Avoid the hazard by introducing additional groups so that no non-<br>overlapping groups remain<br>$A \setminus BC  00  01  11  10 \\ 0 \\ 1  0  0$ • Groups are $\overline{A}C + AB$ which do not overlap<br>- Potential hazard<br>• Introduce the additional term <i>BC</i> to avoid the hazard<br>$\overline{A}C + AB + BC$                                                                                                                                                  |  |  |

| E1.2 Digital Electronics I 8.19 Nov 2007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E1.2 Digital Electronics I 8.20 Nov 2007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |