## **Digital Electronics**

## **Answer Sheet 13**

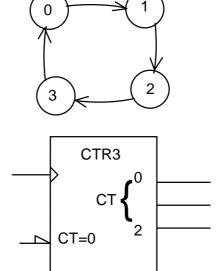

- 1. It can be seen that a down-counter is an up-counter but with the outputs taken from the  $\overline{Q}$  outputs instead of the Q outputs.

- 2. Synchronous CLEAR:

Asynchronous CLEAR:

3.

a)

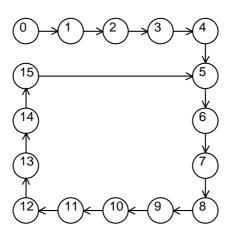

- b) The number of states in one complete cycle is 11. TC and OUT go high once per cycle and, hence, the output frequency in  $16/11~\rm kHz$ .

- c) For N < 15,  $f_{Out} = \frac{16}{16 N} \text{ kHz}$

- d) For N = 15,  $f_{OUt} = 0$  and OUT always equals 1.