## E2.1 – Digital Electronics II

## **Solution to Problem Sheet 4**

(Question ratings: A=Easy, ..., E=Hard. All students should do questions rated A, B or C as a minimum)

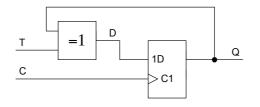

1B. As seen in problem sheet 1, an XOR gate can be used to invert a signal or pass it through unchanged according to whether a control input is high or low.

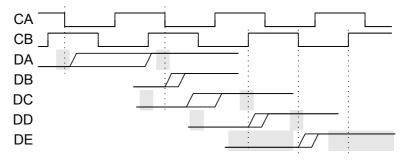

2C. We define t=0 as the falling edge of CA.

| Setup requirement: | $\max(DB\uparrow\downarrow)+12 < \min(CB\uparrow)$<br>$50+22+12 < (13 + \frac{1}{2}T)$<br>$\frac{1}{2}T > 71 \implies f < 7 \text{ MHz}$                  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hold requirement:  | $\max(CB\uparrow) + 27 > \min(T + DB\uparrow\downarrow)$<br>$\frac{1}{2}T+22 + 27 > T + 5+13$<br>$\frac{1}{2}T > 31$ (less severe restriction than above) |

Note the extra T term in the hold requirement: this is because we want the *second* transition of DB to occur >27 ns after CB $\uparrow$ . The Hold requirement is so easily satisfied that it wouldn't normally be necessary to calculate it exactly.

3C.

| µPA →<br>flipflop<br>CA↓=0             | Setu<br>p: | $\max(DA \uparrow \downarrow) +5 < \min(CA \uparrow)$<br>$50+5 < \frac{1}{2}T$<br>$\frac{1}{2}T > 55 \Rightarrow \underline{f < 9}$<br><u>MHz</u> | Hol<br>d: | max(CA↑)+3<<br>min(T+DA↑↓)<br><sup>1</sup> ⁄ <sub>2</sub> T+3< T + 5<br><sup>1</sup> ⁄ <sub>2</sub> T > -2 ☑                      |

|----------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| flipflop →<br>flipflop<br>CA↑=0        | Setu<br>p: | $max(DB\uparrow\downarrow)+5 < min(CB\downarrow)$<br>10+22+5 < ½T+13<br>½T > 24 $\Rightarrow$ f < 21<br>MHz                                       | Hol<br>d: | $max(CB\downarrow)+3 < min(T+DB\uparrow\downarrow)  \frac{1}{2}T+22+3 < T+2+13  \frac{1}{2}T > 10 \implies f < 50  MHz$           |

| flipflop $\rightarrow$<br>µPB<br>CB↓=0 | Setu<br>p: | $max(FB\uparrow\downarrow)+12 < mi$ $n(CB\uparrow)$ $10+12 < \frac{1}{2}T$ $\frac{1}{2}T > 22 \implies f < 23$ MHz                                | Hol<br>d: | $\max(CB\uparrow)+27 < \min(T +FB\uparrow\downarrow)$<br>$\frac{1}{2}T+27 < T+2$<br>$\frac{1}{2}T > 25 \Rightarrow f < 20$<br>MHz |

It can be seen that the critical figure is the setup time for the first flipflop: this is because the microprocessor takes such a long time (up to 50 ns) to output its data.

Question 4 (which doesn't work) and question 5 (which does) show how to relax this constraint. In the third row of the previous table, I have cancelled out the delay of the clock line driver/receiver from the two sides of the inequality. This is only valid if we can assume that the propagation delays for rising and falling edges are the same (not generally true).

4C. The first flipflop now responds to a falling clock edge: this means that  $\mu$ PA now has a full clock cycle to output its data rather than only a half cycle. We have therefore doubled maximum clock frequency of the circuit. (Note that the middle row of this table is unchanged from the previous question).

The problem is that the output from the second flipflop now changes on the rising clock edge and therefore fails to meet the hold time of  $\mu PB$ .

| µPA →<br>flipflop<br>CA↓=0      | Setu<br>p: | $\max(DA \uparrow \downarrow)+5 < \min(T + CA \downarrow)$<br>50+5 < T<br>T > 55 $\Rightarrow$ <u>f &lt; 18 MHz</u> | Hol<br>d: | max(CA↓)+3 <min(d<br>A↑↓)<br/>0+3&lt;5 ☑</min(d<br>                                                                         |

|---------------------------------|------------|---------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| flipflop →<br>flipflop<br>CA↓=0 | Setu<br>p: | $max(DC\uparrow\downarrow)+5 24 \implies f < 21MHz$                                                                 | Hol<br>d: | $max(CB\uparrow)+3 < min(T +DC\uparrow\downarrow)  \frac{1}{2}T+22+3 < T + 2+13  \frac{1}{2}T > 10 \Rightarrow f < 50  MHz$ |

| flipflop →<br>μPB<br>CB↑=0      | Setu<br>p: | $max(DD\uparrow\downarrow)+12 < min(T+CB\uparrow)10+12 < TT > 22 \implies f < 46 MHz$                               | Hol<br>d: | max(CB↑)+27 <min(<br>DD↑↓)<br/><u>2 &gt; 27</u> ⊠</min(<br>                                                                 |

5D. We can fix the hold problem by adding a third flipflop. The last row of the previous table is now replaced by the two rows below and the maximum frequency is now 18 MHz.

| flipflop $\rightarrow$<br>flipflop<br>CB $\uparrow=0$ | Setu<br>p: | $\max(DD \uparrow \downarrow)+5 < \min(CB \downarrow)$ $10+5 < \frac{1}{2}T$ $\frac{1}{2}T > 15 \Rightarrow f < 33$ | Hol<br>d: | $\max(CB\downarrow)+3 < \min(T +DD\uparrow\downarrow)$ $\frac{1}{2}T+3 < T+2$ $\frac{1}{2}T > 1 \implies f < 500$              |

|-------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------|

|                                                       |            | MHz                                                                                                                 |           | MHz                                                                                                                            |

| flipflop →<br>µPB<br>CB↓=0                            | Setu<br>p: | $max(DE\uparrow\downarrow)+12 < min(CB\uparrow)$ $10+12 < \frac{1}{2}T$ $\frac{1}{2}T > 22 \implies f < 23$ MHz     | Hol<br>d: | $\max(CB\uparrow)+27 < \min(T +DE\uparrow\downarrow)$<br>$\frac{1}{2}T+27 < T+2$<br>$\frac{1}{2}T > 25 \implies f < 20$<br>MHz |

The timing of this circuit with a clock period of about 60 ns (16.7 MHz) is shown below with setup/hold windows shaded: