#### Based on slides/material by...

| Topic 12                                                                                                             |              | <ul> <li>J. Rabaey http</li> </ul>                                    | ttp://cas.ee.ic.ac.uk/~kostas<br>://bwrc.eecs.berkeley.edu/Classes/IcBook/ins<br>ted Circuits: A Design Perspective", Prentice                                                             |              |

|----------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| <b>Testing</b><br>Peter Y. K. Cheung<br>Department of Electrical & Electronic Engineering<br>Imperial College London |              | Weste and Ha<br>Perspective", A<br>Recommended R<br>◆ J. Rabaey et. a | //www.cmosvlsi.com/coursematerials.html<br>rris, "CMOS VLSI Design: A Circuits and Syst<br>Addison Wesley<br>eading:<br>al. "Digital Integrated Circuits: A Design Pers<br>dology Insert H |              |

| URL: http://www.ee.ic.ac.uk/pcheung                                                                                  |              | <ul> <li>Weste and Ha<br/>Perspective": (</li> </ul>                  | rris, "CMOS VLSI Design: A Circuits and Syst<br>Chapter 9                                                                                                                                  | tems         |

| Digital Integrated Circuit Design                                                                                    | Topic 12 - 1 | Design for Test                                                       | Digital Integrated Circuit Design                                                                                                                                                          | Topic 12 - 2 |

| Testing                                                                                                              |              |                                                                       | Logic Verification                                                                                                                                                                         |              |

- Testing is one of the most expensive parts of chips

- Logic verification accounts for > 50% of design effort for many chips

- Debug time after fabrication has enormous opportunity cost

- Shipping defective parts can sink a company

- Example: Intel FDIV bug

- Logic error not caught until > 1M units shipped

- Recall cost \$450M (!!!)

- Does the chip simulate correctly?

- Usually done at HDL level

- · Verification engineers write test bench for HDL

- Can't test all cases

- Look for corner cases

- Try to break logic design

- Ex: 32-bit adder

- Test all combinations of corner cases as inputs:

- ► 0, 1, 2, 2<sup>31</sup>-1, -1, -2<sup>31</sup>, a few random numbers

- Good tests require ingenuity

Design for Test

#### **Silicon Debug**

#### **Shmoo Plots**

| <ul> <li>Test the first chips back from fabrication <ul> <li>If you are lucky, they work the first time</li> <li>If not</li> </ul> </li> <li>Logic bugs vs. electrical failures <ul> <li>Most chip failures are logic bugs from inadequate simulation</li> <li>Some are electrical failures</li> <li>Crosstalk</li> <li>Dynamic nodes: leakage, charge sharing</li> <li>Ratio failures</li> </ul> </li> <li>A few are tool or methodology failures (e.g. DRC)</li> </ul> |              |           | How to diagnose failures?  Hard to access chips Picoprobes Electron beam Laser voltage probing Built-in self-test Shmoo plots Vary voltage, frequency Look for cause of electrical failures | Fininge on the 4<br>* in<br>1.1 * * * * * * * * * * * * * * * * * * | h (A), fragmeny increase going at<br>tatam, increase (A) a right<br>dicates a folder:<br>1.0                                                                                                      |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| <ul> <li>Fix the bugs and fabricate a corrected chip</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |              |           |                                                                                                                                                                                             | Walf<br>Fals at 1 certain what<br>Coupling, charge share, races     | "Revene speadpath"<br>Increase in voltage rokeves frasquarey<br>Speedpath, kolago<br>1.0<br>1.2<br>1.2<br>1.2<br>1.4<br>1.5<br>1.6<br>1.6<br>1.6<br>1.6<br>1.6<br>1.6<br>1.6<br>1.6<br>1.6<br>1.6 |         |

| asign for Test Digital Integrated Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                         | Topic 12 - 5 | Design fo | r Test                                                                                                                                                                                      | Digital Integrated Circuit Design                                   |                                                                                                                                                                                                   | Topic 1 |

**Manufacturing Test**

- A speck of dust on a wafer is sufficient to kill chip

- *Yield* of any chip is < 100%

- Must test chips after manufacturing before delivery to customers to only ship good parts

- Manufacturing testers are very expensive

- Minimize time on tester

- Careful selection of test vectors

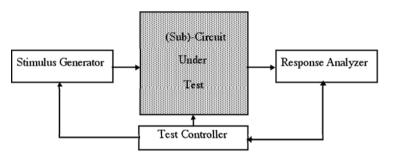

# Validation and Test of Manufactured Circuits

#### **Goals of Design-for-Test (DFT)**

Make testing of manufactured part swift and comprehensive

#### **DFT Mantra**

Provide controllability and observability

#### **Components of DFT strategy**

- Provide circuitry to enable test

- Provide test patterns that guarantee reasonable coverage

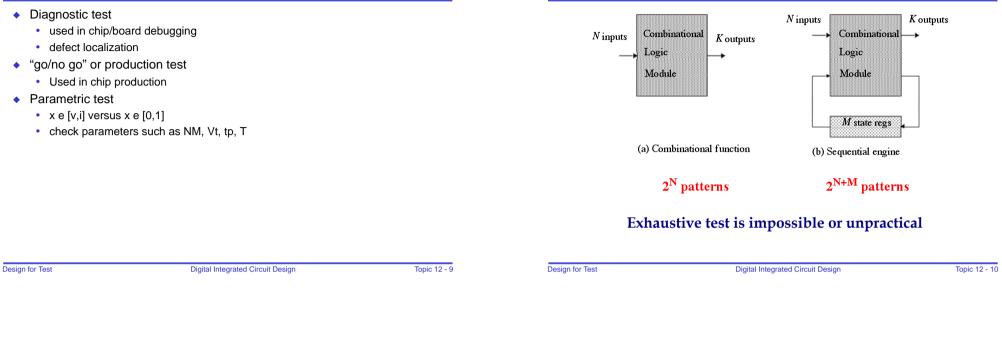

#### **Test Classification**

#### **Design for Testability**

# **Design for Test**

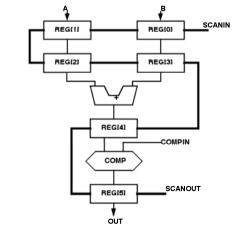

- Design the chip to increase observability and controllability

- If each register could be observed and controlled, test problem reduces to testing combinational logic between registers.

- Better yet, logic blocks could enter test mode where they generate test patterns and report the results automatically.

# Controllability/Observability

- Combinational Circuits: controllable and observable - relatively easy to determine test patterns

- Sequential Circuits: State! Turn into combinational circuits or use self-test

- Memory: requires complex patterns Use self-test

#### **Generating and Validating Test-Vectors**

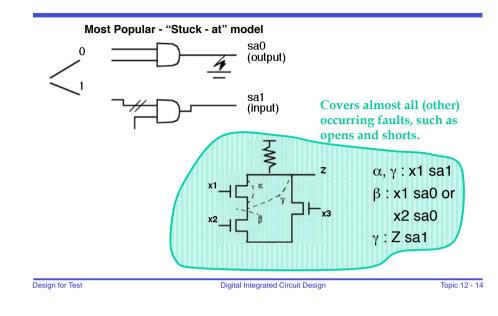

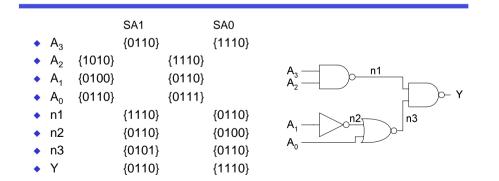

#### Fault Models

- Automatic test-pattern generation (ATPG)

- for given fault, determine excitation vector (called test vector) that will propagate error to primary (observable) output

- majority of available tools: combinational networks only

- sequential ATPG available from academic research

- Fault simulation

- · determines test coverage of proposed test-vector set

- simulates correct network in parallel with faulty networks

- Both require adequate models of faults in CMOS integrated circuits

| Design for Test | Digital Integrated Circuit Design | Topic 12 - 13 |

|-----------------|-----------------------------------|---------------|

|                 |                                   |               |

|                 |                                   |               |

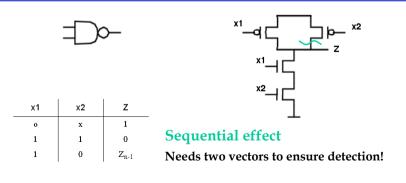

#### Problem with stuck-at model: CMOS open fault

Other options: use stuck-open or stuck-short models This requires fault-simulation and analysis at the switch or transistor level - Very expensive!

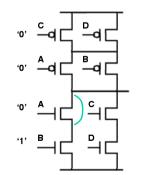

#### Problem with stuck-at model: CMOS short fault

Causes short circuit between Vdd and GND for A=C=0, B=1

Possible approach: Supply Current Measurement (IDDQ) but: not applicable for gigascale integration

#### **Test Pattern Generation**

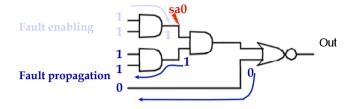

#### **Path Sensitization**

- Manufacturing test ideally would check every node in the circuit to prove it is not stuck.

- Apply the smallest sequence of test vectors necessary to prove each node is not stuck.

- Good observability and controllability reduces number of test vectors required for manufacturing test.

- · Reduces the cost of testing

- · Motivates design-for-test

Goals: Determine input pattern that makes a fault controllable (triggers the fault, and makes its impact visible at the output nodes)

#### Techniques Used: D-algorithm, Podem

#### **Test Example**

Minimum set: {0100, 0101, 0110, 0111, 1010, 1110}

#### **Test Approaches**

- Ad-hoc testing

- Scan-based Test

- Self-Test

- Problem is getting harder

- increasing complexity and heterogeneous combination of modules in systemon-a-chip.

- Advanced packaging and assembly techniques extend problem to the board level

Topic 12 - 19

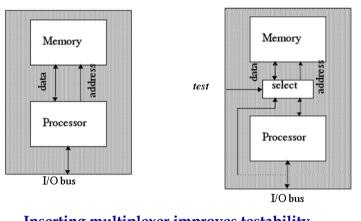

# **Ad-hoc Test**

#### Inserting multiplexer improves testability

| Design for Test | Digital Integrated Circuit Design | Topic 12 - 21 |

|-----------------|-----------------------------------|---------------|

| 0               |                                   |               |

|                 |                                   |               |

|                 |                                   |               |

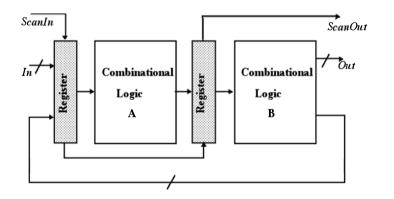

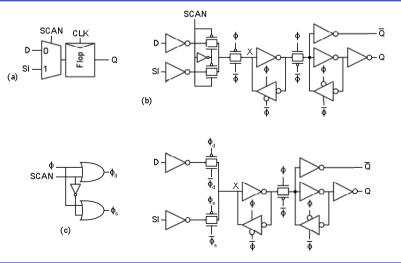

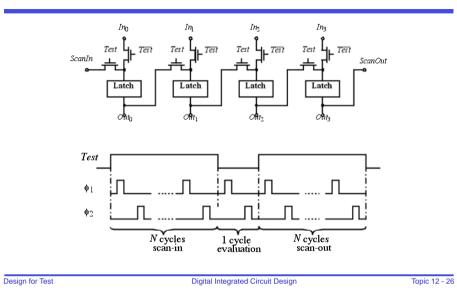

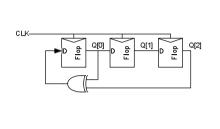

# **Scan-based Test**

#### • Convert each flip-flop to a scan register CLK Only costs one extra multiplexer Normal mode: flip-flops behave as usual Flop SI Q • Scan mode: flip-flops behave as shift register D Contents of flops can be scanned out and new values scanned in Logic Cloud Logic Cloud

Scan

Design for Test

Digital Integrated Circuit Design

Topic 12 - 22

outouts

# Scannable Flip-flops

Topic 12 - 23

Design for Test

#### Design for Test

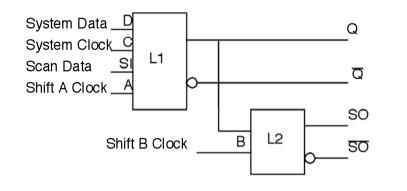

#### Polarity-Hold SRL (Shift-Register Latch)

Introduced at IBM and set as company policy

| Design for Test | Digital Integrated Circuit Design | Topic 12 - 25 |

|-----------------|-----------------------------------|---------------|

|                 |                                   |               |

|                 |                                   |               |

# **Scan-Path Testing**

Partial-Scan can be more effective for pipelined datapaths

#### **Scan-based Test**—Operation

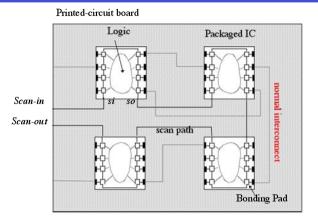

#### **Boundary Scan**

- Testing boards is also difficult

- Need to verify solder joints are good

- Drive a pin to 0, then to 1

- ➤ Check that all connected pins get the values

- Through-hold boards used "bed of nails"

- SMT and BGA boards cannot easily contact pins

- Build capability of observing and controlling pins into each chip to make board test easier

# **Boundary Scan (JTAG)**

# **Boundary Scan Example**

CHIP C

Serial Data Out

CHIP D

Package Interconnect

#### Board testing becomes as problematic as chip testing

| Design for Test | Digital Integrated Circuit Design | Topic 12 - 29 | Design for Test | Digital Integrated Circuit Design | Topic 12 - 30 |

|-----------------|-----------------------------------|---------------|-----------------|-----------------------------------|---------------|

|                 |                                   |               |                 |                                   |               |

#### **Boundary Scan Interface**

- Boundary scan is accessed through five pins

- TCK: test clock

- TMS: test mode select

- TDI: test data in

- TDO: test data out

- TRST\*: test reset (optional)

- Chips with internal scan chains can access the chains through boundary scan for unified test strategy.

#### **Built-in Self-test**

- Built-in self-test lets blocks test themselves

- Generate pseudo-random inputs to comb. logic

Serial Data In

• Combine outputs into a syndrome

CHIP B

CHIP A

lOpad and Boundary Scar Cell

• With high probability, block is fault-free if it produces the expected syndrome

#### Self-test

# Rapidly becoming more important with increasing chip-complexity and larger modules

# Design for Test Digital Integrated Circuit Design

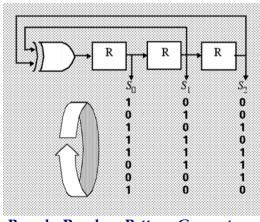

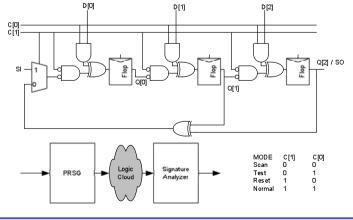

# Linear-Feedback Shift Register (LFSR)

#### **Pseudo-Random Pattern Generator**

#### PRSG

- Linear Feedback Shift Register

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

| Step | Q             |

|------|---------------|

| 0    | 111           |

| 1    | 110           |

| 2    | 101           |

| 3    | 010           |

| 4    | 100           |

| 5    | 001           |

| 6    | 011           |

| 7    | 111 (repeats) |

Design for Test

Digital Integrated Circuit Design

Topic 12 - 34

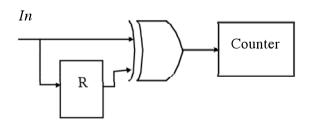

# Signature Analysis

# Counts transitions on single-bit stream **=** Compression in time

Topic 12 - 33

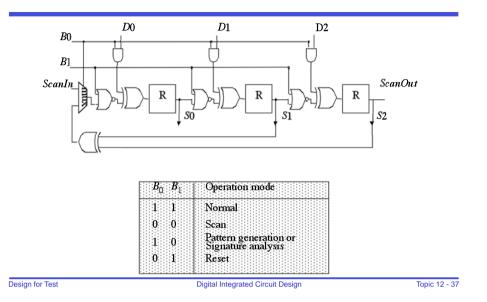

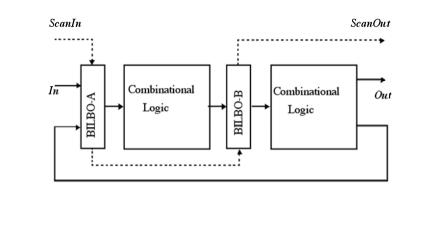

#### **BILBO**

#### **BILBO Application**

**BILBO**

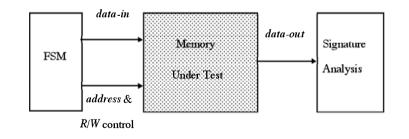

- Built-in Logic Block Observer

- Combine scan with PRSG & signature analysis

#### **Memory Self-Test**

Digital Integrated Circuit Design

Patterns: Writing/Reading 0s, 1s, Walking 0s, 1s Galloping 0s, 1s

Design for Test

Topic 12 - 38

#### **Low Cost Testing**

#### **TestosterICs**

- If you don't have a multimillion dollar tester:

- Build a breadboard with LED's and switches

- Hook up a logic analyzer and pattern generator

- Or use a low-cost functional chip tester

- Ex: TestosterICs functional chip tester

- Designed by clinic teams and David Diaz at HMC

- Reads your IRSIM test vectors, applies them to your chip, and reports assertion failures

Digital Integrated Circuit Design

Topic 12 - 42

| Design for Test Digital Integrated Circuit Design Topic 12 - 41 |

|-----------------------------------------------------------------|

| 5 m 15 m 15 m 15 m 15 m 16 m 16 m 16 m 1                        |

|                                                                 |

# Summary

- Think about testing from the beginning

- Simulate as you go

- Plan for test after fabrication

- "If you don't test it, it won't work! (Guaranteed)"